# ED29116

DESIGNING

WITH THE Am29116

16-BIT

BIPOLAR MICROPROCESSOR

LECTURE VOLUME I

#### ED29116

"Designing with the Am29116 16-Bit Bipolar Microprocessor"

bу

Barbara Albert Arndt Bode, Dr. rer. nat. J.W. Locke, Ph.D.

March 1983

Customer Education Center Advanced Micro Devices, Inc.

$\cap$  .

ED29116

DAY 1

CHAPTER Ø

INTRODUCTION

#### Designing with the AM29116

The AM29116 combines the advantages of the AM2900 bitslice microprocessor family:

- bipolar (fast)

- microprogrammable (flexible)

- LSI (low cost and reliable)

- industry standard (many circuits and second sources)

- development aids

(hardware/firmware/software)

with:

- a very high degree of integration (16 Bit,...)

- special purpose features (CRC,...)

- very high speed (100 ns cycle)

Remember the advantages of a bipolar, microprogrammable, industry-standard LSI Family with development aids (as presented in ED2900A, EDSYS29).

From such a Family of parts you may construct:

- fast machines (125 ns cycle time)

- with almost any desired architecture

- with any desired instruction set

- allowing "soft" upgrades

(field changes, adaptations, system expansions)

simply by changing the contents

of the microprogram memory

- with relatively small parts count (50 DIPS) allowing for low cost and high reliability

- with design time shortened by parallel hardware/firmware development on System 29

- easily debugged with hardware & software aids

- with documentation automatically enforced by programming techniques used on System 29

As you design with an the industry-standard Am2900 Family:

- your task is facilitated by the largest number of special purpose circuits fully compatible with your application (we will see the part numbers on the next pages)

- the Am2900 Family is constantly expanding (and is an increasingly-active product line)

- as AMD's technology advances you get

pin-compatible faster devices

(e.g. Am2901 / Am2901A / Am2901B / Am2901C / ...!)

- you have the largest number of second sources (but AMD products are faster and more reliable!!)

# Am2900 Product Family

| Part Number     | Description                                    |

|-----------------|------------------------------------------------|

|                 |                                                |

| Am29Ø1          | 4-bit Bipolar Microprocessor Slice             |

| Am29Ø2          | High-Speed Look-Ahead Carry Generator          |

| Am29Ø3          | 4-bit Bipolar Microprocessor Slice             |

| Am29Ø4          | Status and Shift Control Unit                  |

| Am29Ø5          | Quad 2-Input Bus Transceiver, O.C.             |

| Am29Ø6          | Quad 2-Input Bus Transceiver, O.C.             |

| Am29Ø7/29Ø8     | Quad Bus Transceiver with Interface Logic      |

| Am29Ø9          | 4-Bit Microprogram Sequencer Slice             |

| Am291Ø          | 12-Bit Microprogram Sequencer                  |

| Am2911          | 4-Bit Microprogram Sequencer Slice             |

| Am2912          | Quad Bus Transceiver                           |

| Am2913          | 8-Input Priority Interrupt Expander            |

| Am2914          | 8-Input Vectored Priority Interrupt Controller |

| Am2915          | Quad Bus Transceiver, Three-State              |

| Am2916          | Quad Bus Transceiver, Three-State              |

| Am2917          | Quad Bus Transceiver, Three-State              |

| Am2918/Am29LS18 | Quad D-Register                                |

| Am2919          | Quad D-Register with Dual Three-State Outputs  |

| Am292Ø          | Octal D-Type Flip-Flop                         |

| Am2921          | One-of-Eight Decoder with Polarity Control     |

| Am2922          | 8-Input Multiplexer with Control Register      |

|                 |                                                |

# Am2900 Product Family (continued)

| Part Number | <u>Description</u>                                |

|-------------|---------------------------------------------------|

| Am2923      | 8-Input, Three-State Multiplexer                  |

|             | Three-Line to Eight-Line Decoder/Demultiplexer    |

| Am2924      | - · · · · · · · · · · · · · · · · · · ·           |

| Am2925      | System Clock Generator and Driver                 |

| Am2926      | Quad Bus Driver/Receiver, Inverting               |

| Am2927/2928 | Quad 3-State Bus Transceiver with Clock Enable    |

| Am2929      | Quad Bus Driver/Receiver, Non-Inverting           |

| Am293Ø      | 4-Bit Program Control Unit Slice                  |

| Am2932      | 4-Bit Program Control Unit / Push-Pop Stack Slice |

| Am294Ø      | DMA Address Generator                             |

| Am2942      | Programmable Timer/Counter/DMA Address Generator  |

| Am2946/2947 | Octal 3-State Bidirectional Bus Transceiver       |

| Am2948/2949 | Octal 3-State Bidirectional Bus Transceiver       |

| Am295Ø/2951 | 8-Bit Bidirectional I/O Port with Handshake       |

| Am2952/2953 | 8-Bit Bidirectional I/O Port                      |

| Am2954/2955 | Octal Register, Three-State                       |

| Am2956/2957 | Octal Latch, Three-State                          |

| Am2958/2959 | Octal Buffer/Line Driver/Line Receiver, 3-State   |

| Am296Ø      | 16-Bit Memory Error Detection & Detection Unit    |

| Am2961/2962 | 4-Bit Error Correction Multiple Bus Buffer        |

| Am2964      | Dynamic Memory Controller                         |

| Am2965      | Octal RAM Driver, Inverting                       |

| Am2966      | Octal RAM Driver, Non-Inverting                   |

# Am2900 Product Family (continued)

| <u>Part Number</u> | Description                                      |

|--------------------|--------------------------------------------------|

| Am29112            | Interruptable 8-bit Microprogram Sequencer Slice |

| Am29116            | 16-Bit Bipolar Microprocessor                    |

| Am292Ø3            | 4-Bit Bipolar Microprocessor Slice               |

| Am295Ø1            | Microprogrammable Signal Processor               |

| Am29516            | 16 x 16-bit Parallel Multiplier                  |

| Am2952Ø            | Quad Octal Multilevel Pipeline Register          |

| Am29521            | Quad Octal Multilevel Pipeline Register          |

| Am2954Ø            | Programmable FFT Address Sequencer               |

| Am297ØØ/297Ø1      | 64-Bit Non-Inverting RAM                         |

| Am297Ø2/297Ø3      | 64-Bit Schottky RAM                              |

| Am297Ø5            | 16-Word x 4-bit Two Port RAM                     |

| Am297Ø7            | 16-Word x 4-bit Two Port RAM                     |

| Am2972Ø/29721      | 256-Bit Low-Power Schottky RAM                   |

| Am2975Ø/29751A     | 32-Word by 8-Bit PROM                            |

| Am2976ØA/29761A    | 256-Word by 4-Bit PROM                           |

| Am29770/29771      | 2048-Bit Generic Series Bipolar PROM             |

| Am29774/29775      | 4096-Bit Registered PROM                         |

| Am298Ø3A           | 16-Way Branch Control Unit for Am29Ø9            |

| Am29811A           | Next Address Control Unit for Am2911             |

#### Am29116 Applications - a Preview

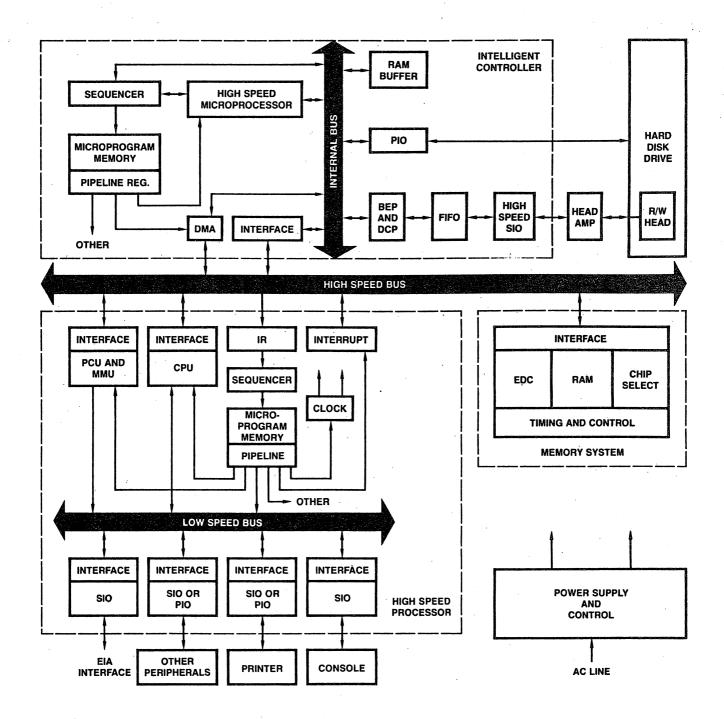

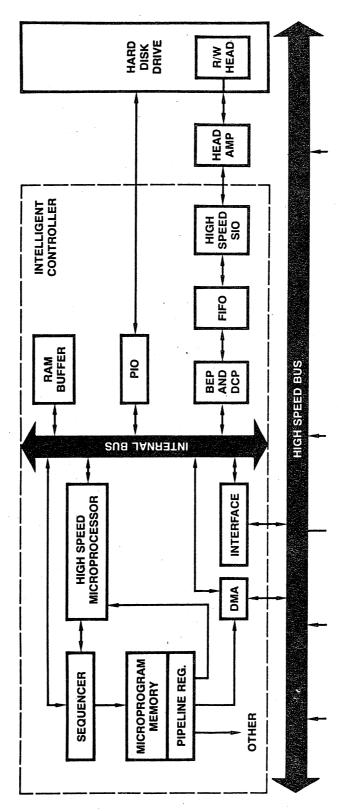

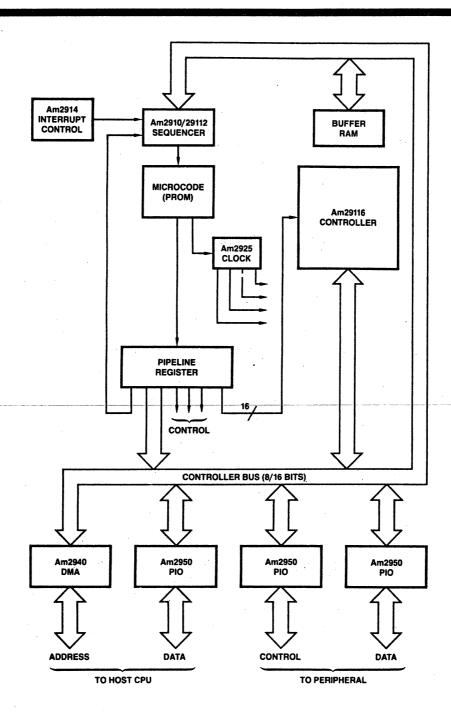

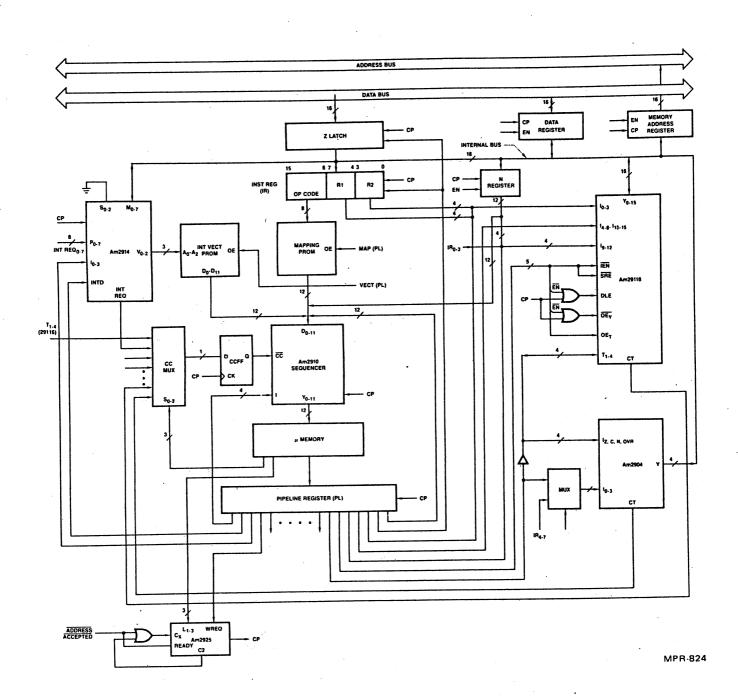

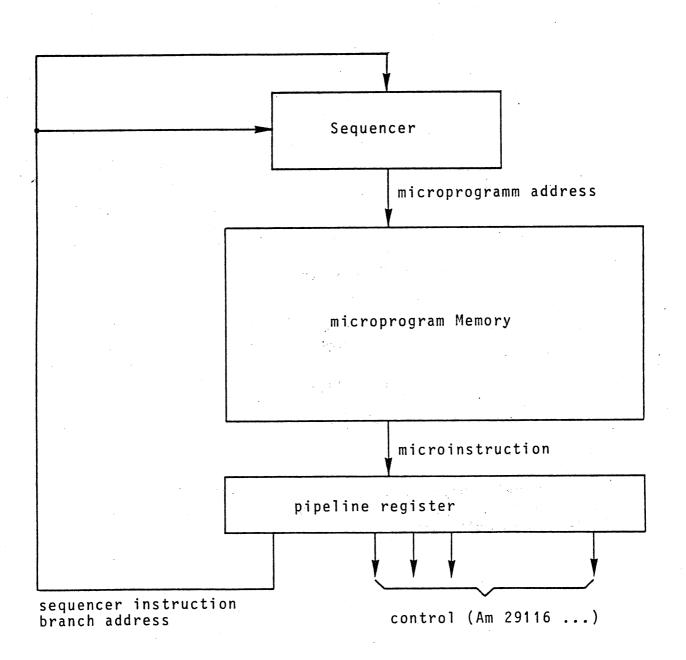

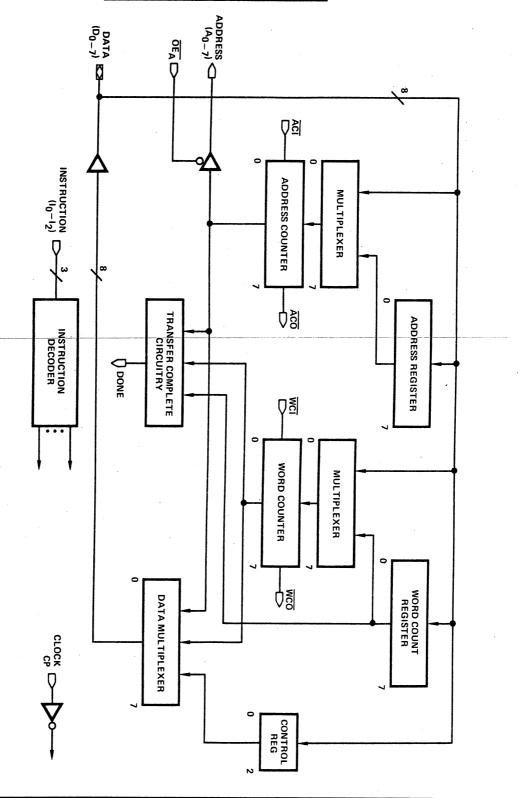

Let's have a look at a complete high performance microprogrammed computer system.

The Am29116 is useful in many different application areas. Typical application examples might include using Am29116:

- as a high speed microprocessor within an intelligent controller

- as the CPU of a high speed processor

- as a high-speed graphics controller

#### Typical Processor and Controller

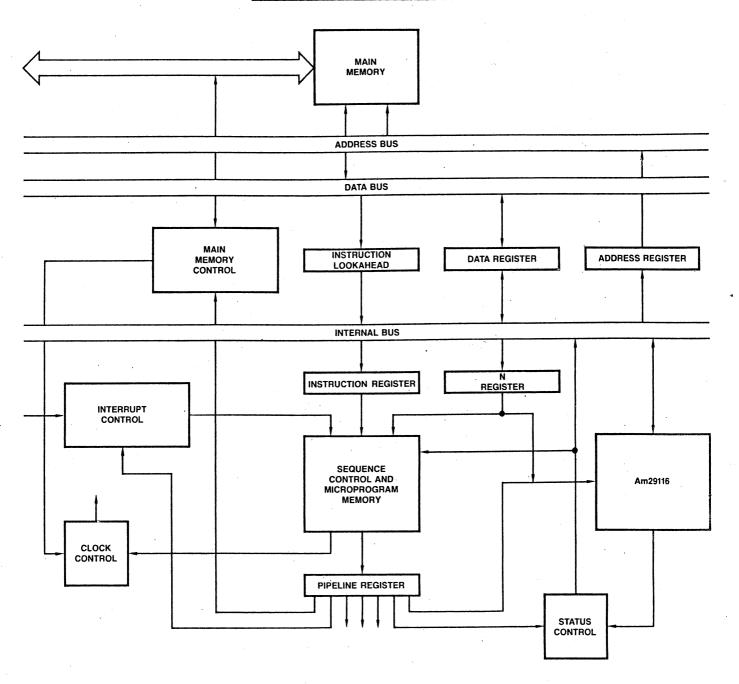

#### The Am29116 as a 16-Bit CPU

MPR-819

Structure of an Intelligent Controller

#### Am29116 Applications - a Preview (continued)

- The Am29116 architecture and instruction set is optimized for high performance peripheral controllers:

- graphics controllers

- disk controllers

- communication controllers

- front-end concentrators

- modems

- Am29116 bit-oriented, rotate-and-merge, rotate-and-compare, and CRC-calculation instructions are particularly useful in such controller applications.

- The Am29116 also performs well for general purpose CPU applications (especially when combined with the Am29516 16 x 16 multiplier) as it has a complete arithmetic and logic instruction set.

#### Am29116 Controller Applications

The original Am2900 Family products are used in many controller applications due to their features such as microprogrammability, short cycle times, arithmetic and logic instructions etc.

But many controllers require additional features:

- 1) bit manipulation

- 2) character or byte-wide data handling

- 3) CRC calculations for error control

- 4) a generally richer instruction set

- 5) faster execution

With the Am2901 and enough software you can accomplish 1) through 4) but some functions will execute too slowly.

AMD's Am29116 extends the Am2900 Family to meet all of these controller requirements!

## Some Parts of Interest for Controllers

| 29116   | 16-Bit Bipolar Microprocessor |

|---------|-------------------------------|

| 29112   | Interruptable Sequencer       |

| 2914    | Interrupt Controller          |

| 2940/42 | DMA Address Generator         |

| 295Ø/51 | Parallel I/O Port             |

| 952Ø    | Burst Error Processor         |

| 29XXX   | Asparagus                     |

#### Controller Requirements

Commonly Needed Operations:

- Moving Data from Port to Port

- Testing Incoming Signals (Bits) such as:

- Status

- Commands

- Generating Outgoing Signals (Bits) such as:

- Status

- Commands

- Timing Signals

- Rotating and Shifting

- Executing integer arithmetic (usually 16-bit signed values)

- Assessing priority

### Some of AMD's Design Goals for the Am29116

Microprogrammable

16 Bits

100ns Microcycle

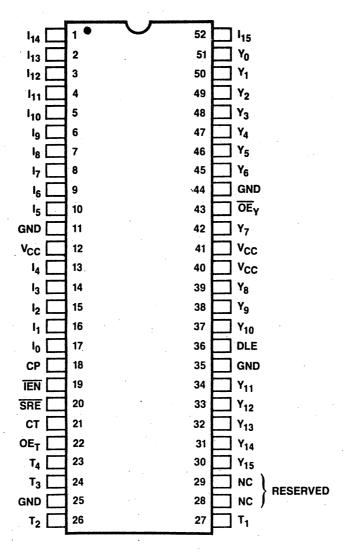

52-Pin Dip

+ 5V only

TTL Compatible I/O

Extensive instruction set

Many registers

Hardware for faster shifting, priority-encoding and Cyclic Redundancy Check calculations

### CHAPTER 1

### Presenting the Am29116

- Architecture

- Instruction Set

- Timing

- Definition File

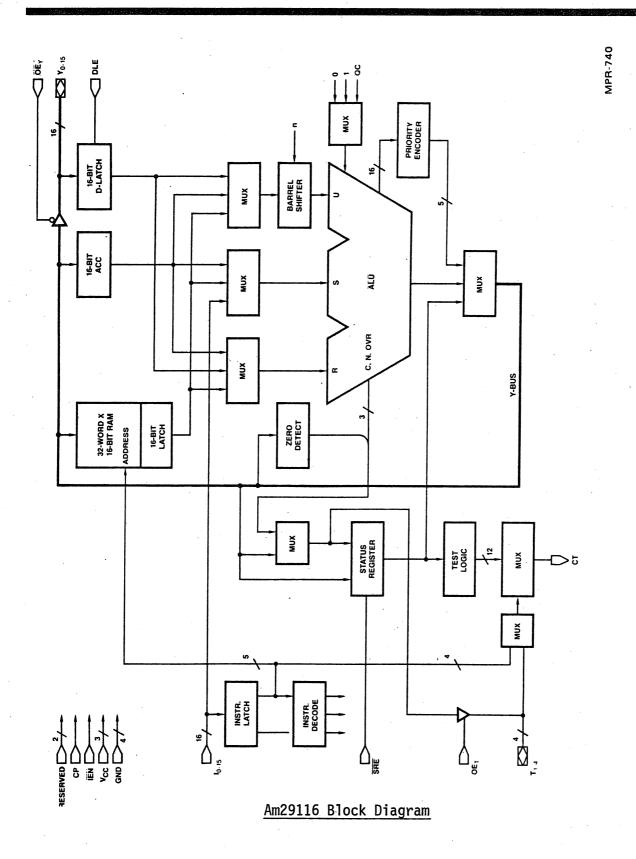

#### Am29116 Outstanding Features

- Emitter-coupled logic (ECL) internally for speed

- TTL I/O for easy interfacing

- 16-bit data paths:

- 16-bit ALU

- . full carry lookahead

- . 16-bit Word Mode or 8-bit Byte Mode

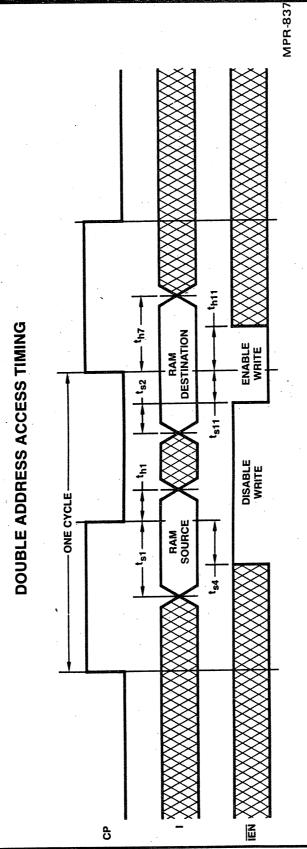

- 32-word x 16-bit register file (here called RAM)

- . single port architecture

- different source and destination addresses are selectable by using an additional, external multiplexer

- 16-bit data latch

- 16-bit barrel shifter

- . works in byte or word mode

- . rotates up 1 to 15 bits in one cycle (remember: up shift by n bits is equivalent to down shift by (16-n) bits)

#### Am29116 Outstanding Features (continued)

- 8-bit status register

- Condition code generator/multiplexer

12 different test conditions

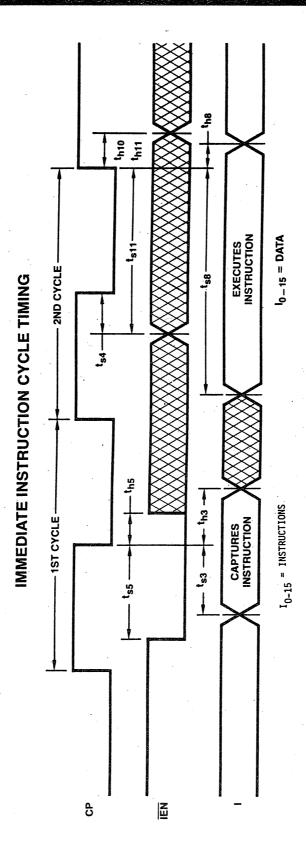

- Immediate instruction capability:

- . first microcycle instruction is latched

- . second microcycle immediate data is read via the instruction lines

- CRC generation

- . any polynomial of 16 bits or less (80% of CRC applications require a 16-bit polynomial)

- powerful instruction set

- fixed width

- fast (100 ns cycle time)

- 52-pin DIP

- single 5 Volt power supply

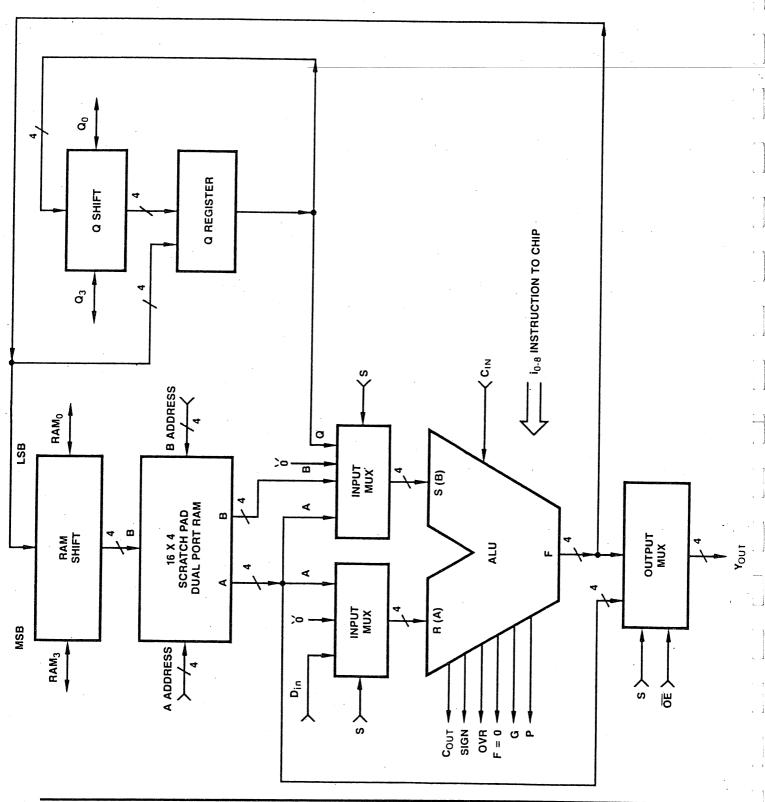

Am29116 ARCHITECTURE

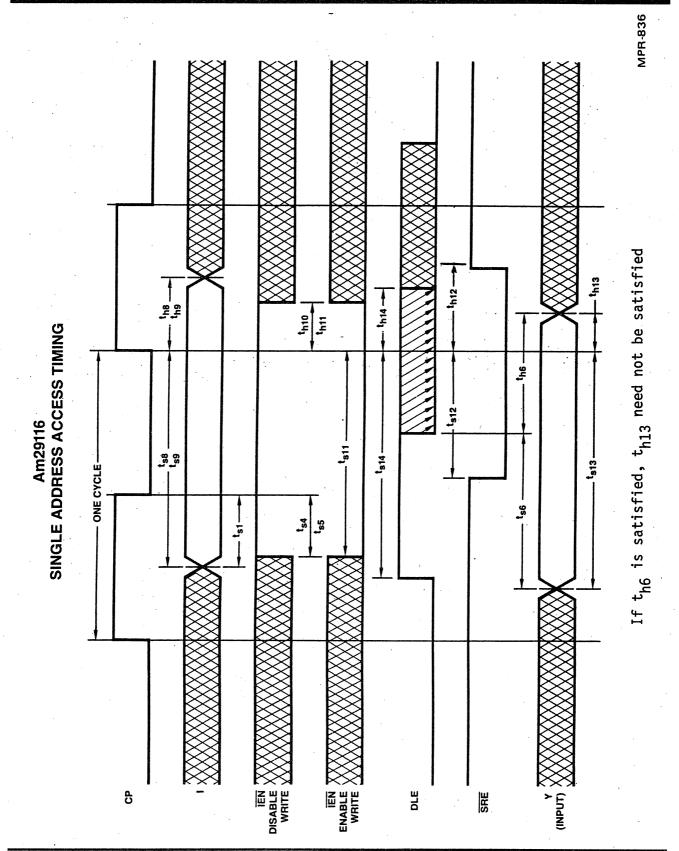

#### 32-Word x 16-bit Register File - RAM

- Single Port

i.e.: only one of the two source operands

can come from the RAM

- 16-bit latch at RAM output:

. transparent when clock (CP) is high

- . latched when clock goes low

- Data is written to RAM:

- . when  $\overline{\text{CP}}$  is low AND  $\overline{\text{IEN}}$  is low (instruction enable) AND RAM is the destination of the instruction

- In Byte Mode: Instructions alter only the lower 8 bits of a register

- In Word Mode: Instructions alter all 16 bits of a register

- With extended timing and an external multiplexer:

The RAM address can be changed during an instruction.

(permitting different source and destination registers)

#### Accumulator - ACC

- 16-bit edge-triggered register

- Accepts data on rising edge of clock: provided IEN is low and ACC is the destination of the destination

- Responds to Byte Mode instructions and to Word Mode instructions

#### Data Latch - D-Latch

- 16 bit level-controlled register

- Accepts data from the external Y-Bus

- Transparent when DLE input is high (data latch enable)

- Latched when the DLE input is low:

- latches all 16 bits at once

- cannot latch a byte only

#### Barrel Shifter

- Rotates the "U"-input to the ALU

- Can rotate data from

- RAM

- ACC

- D-latch

- Word Mode: Rotates up 1 to 15 bits in a single microcycle

- Byte Mode: Rotates up 1 to 7 bits in a single microcycle (only the lower byte is altered)

#### Arithmetic Logic Unit - ALU

- High speed ALU (full carry lookahead across all 16 bits)

- 16 bits wide

- One, two or three operands

- Executes all of the usual one- and two-operand functions:

Pass AND, NAND, OR, NOR, EXOR, EX-NOR Addition, Subtraction Complement, Negate

- Executes three-operand instructions:

- rotate and merge

- masked rotate and compare

- All of these operations function in Word or Byte Mode

- Includes hardware for Cyclic Redundancy Check calculations

#### Arithmetic Logic Unit - ALU (continued)

• Produces three status outputs:

C N OVR

Carry Negative Overflow

- Z status is generated by separate zero-detect logic

- Carry-in multiplexer allows the selection of: zero, one, or the stored carry (QC)

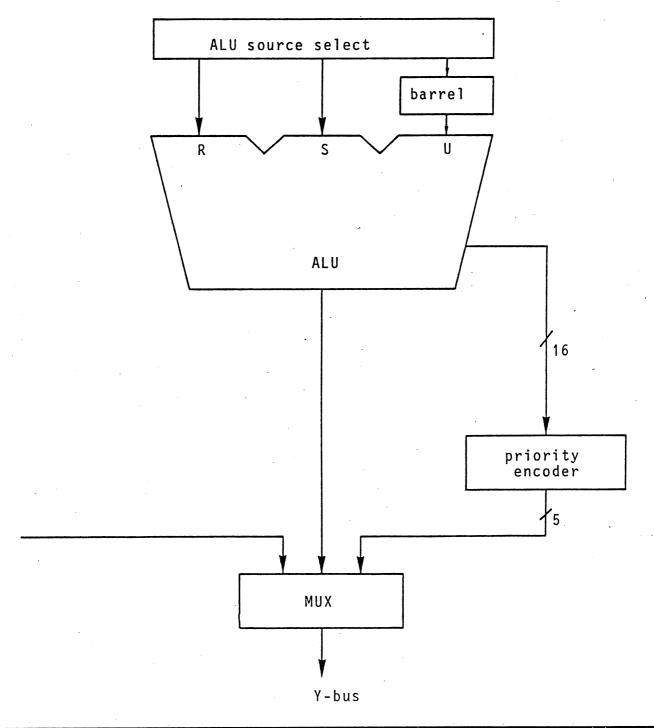

#### Priority Encoder

- Produces a binary-weighted code indicating the location of the highest order <u>one</u> at its input

- Operates on the output of the ALU:

operand AND mask

- Produces a 5-bit result

- Word and Byte Mode are available

#### Status Register

• Holds an 8-bit status word:

with content  $Q_i$  for i = 0, ..., 7.

| Flag3   Flag2   Flag1   LINK   OVR   N   C   Z |

|------------------------------------------------|

|------------------------------------------------|

- Flag1-Flag3: user-definable flags

- LINK: shift-linkage bit

OVR: overflow

- N: negative

C: carry

· Z: zero

- Most instructions update the lower 4 bits of the status register when SRE and IEN are both low

- Certain instructions do not alter status:

- . NOP

- . Save-Status

- . Test-Status

- The LINK bit is updated after each shift

- The user-definable flags are altered only by a Set-Status, Reset-Status or a Word-Mode Load-Status Instruction

- Link status is updated after each shift

#### Status Register (continued)

- Loaded from internal Y-bus

- Saved via internal Y-bus

- ullet The status register may be a source:

- in Word Mode ...

Any 16-bit register:

| Ø | Ø | Ø | Ø | Ø | Ø | Ø | Ø | S | S | S | S | S | S | Š | S | - |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

|   |   |   |   |   |   |   |   | 1 |   |   |   |   | _ |   | • |   |

Zero fills high byte

- in Byte Mode ...

Any 16-bit register:

|           |   |   |   |   |   | - |   |   |

|-----------|---|---|---|---|---|---|---|---|

| unchanged | S | S | S | S | S | S | S | S |

Alters only lower byte

$\bullet$  The lower 4 status bits are available on the T-bus when  $\text{OE}_T$  is high

#### Condition-Code Generator/Multiplexer

- Generates 12 condition-code test signals

- The MUX selects one of them & puts it on the CT output

- The MUX can be controlled in 2 different ways:

- by a TEST instruction (which takes a microcyle to execute)

- or by the use of the T-bus as an input (requires wider microword but allows the simultaneous execution of any instruction)

### Tri-State Buffers

- Bidirectional 16-bit Y-bus

- enabled when  $\overline{\text{OE}}_{\gamma}$  is low

- Bidirectional 4-bit T-bus

- enabled when  $OE_T$  is high

- makes OVR,N,C,Z available

- with the T-bus output disabled ( $OE_T$  low) you can drive the T-bus from an external source to select the test condition

#### Instruction Latch and Decoder

- Normally transparent for all instructions except those specifying immediate data

- On receiving an instruction requiring immediate data

- the instruction is latched on the first cycle

- on the next cycle, the instruction lines are used as data that is conveyed to the S-input of the ALU

Am2901 4-Bit Microprocessor Slice

It is instructive to compare the Am2901 and the Am29116 processors.

#### Am29Ø1 and Am29116 Compared

Am29116

Am2901

• 16-bit fixed width

4-bit slice

Fewer external lines

- lower connection complexity

- no delay between slices

Flexibility in word length

16 bits is ideal for controllers and many other applications

• 32 registers

16 registers

Reduces the number of main memory accesses

The availability of the ACC helps to offset the limitation of a single port. By having a single port, 5 pins are saved (that would have carried the second RAM address).

Expandable to two register address structure with an

external MUX, an additional 5-bit microinstruction field

and extended timing

Two-Port Architecture

## Am2901 and Am29116 Compared (continued)

Am29116

Am29Ø1

• 16-bit barrel shifter

Very fast (rotates 1 to 15 bits per microcycle)

8-bit status register3 user-definable flag bits

Q-shifter, ALU-shifter

Slower: 1 bit per cycle

Does support arithmetic (multiplication and double precision)

4-bit status register via additional, external hardware such as Am29Ø4

• Condition-Code Generator/MUX

Allows testing of 12 conditions on chip for minimum delay

You can extend the number of tests by using the T-bus to output OVR,N,C,Z to an external device such as an Am2904.

Am29116 INSTRUCTION SET

# Am29116 Instruction Set

### 11 Types of Instructions:

- Single Operand

- Two Operand

- Single-Bit Shift

- Bit-Oriented

- Rotate by n Bits

- Rotate & Merge

- Rotate & Compare

- Prioritize

- CRC (cyclic redundancy check)

- Status

- No-Op

### 3 Types of Data:

- Bit

- Byte

- Word

## **ALU Sources**

RAM

ACC

D-Latch

Immediate

## **ALU** Destinations

RAM

ACC

None (i.e. no destination on the Am29116 itself. The ALU output is always put on the Y-bus, however)

## Operand Source/Destination Combinations

| Instruction<br>Type | Operand<br>Combinations (note                                   | 1)                                              |  |  |  |

|---------------------|-----------------------------------------------------------------|-------------------------------------------------|--|--|--|

|                     | Source (R/S)                                                    | Destination                                     |  |  |  |

| Single<br>Operand   | RAM (note 2) ACC D D (ØE) (note 3) D (SE) (note 3) I (note 4) Ø | RAM<br>ACC<br>Y-bus<br>Status<br>ACC and Status |  |  |  |

| ,                   | Destination                                                     |                                                 |  |  |  |

| Two<br>Operand      | RAM ACC RAM I D RAM D ACC ACC I D I                             | RAM<br>ACC<br>Y-bus                             |  |  |  |

- Notes: 1. When there is no dividing line between the R and S operands or between source and destination, the two must be used as a given pair. But where there exists such a separation, any combination of them is possible.

- 2. In the single-operand instruction, RAM cannot be used when both ACC and Status are designated as destinations.

- 3. ØE = zero extended, SE = sign extended.

- 4. "I" indicates immediate data

| Instruction      | Operand Combinations |             |  |  |  |  |  |

|------------------|----------------------|-------------|--|--|--|--|--|

|                  | Source (U)           | Destination |  |  |  |  |  |

|                  | RAM                  | RAM         |  |  |  |  |  |

|                  | ACC                  | ACC         |  |  |  |  |  |

| Single-bit Shift | ACC                  | Y-bus       |  |  |  |  |  |

| •                | D                    | RAM         |  |  |  |  |  |

|                  | D                    | ACC         |  |  |  |  |  |

| •                | D                    | Y-bus       |  |  |  |  |  |

|                  | Source (U)           | Destination |  |  |  |  |  |

|                  | RAM                  | RAM         |  |  |  |  |  |

| Rotate by n Bits | ACC                  | ACC -       |  |  |  |  |  |

|                  | D                    | Y-bus       |  |  |  |  |  |

|                  | Source (R/S)         | Destination |  |  |  |  |  |

|                  | RAM                  | RAM         |  |  |  |  |  |

| Bit-Oriented     | ACC                  | ACC         |  |  |  |  |  |

|                  | D                    | Y-bus       |  |  |  |  |  |

| Instruction<br>Type      |                                | ns                             |                                        |  |

|--------------------------|--------------------------------|--------------------------------|----------------------------------------|--|

|                          | Rotated<br>Source (U)          | Mask (S)                       | Non-Rotated<br>Destination             |  |

| Rotate<br>and<br>Merge   | D<br>D<br>D<br>D<br>ACC<br>RAM | I<br>RAM<br>I<br>ACC<br>I<br>I | ACC<br>ACC<br>RAM<br>RAM<br>RAM<br>ACC |  |

| ·                        | Rotated<br>Source (U)          | Mask (S)                       | Non-Rotated<br>Destination             |  |

| Rotate<br>and<br>Compare | D<br>D<br>D<br>RAM             | I<br>I<br>ACC<br>I             | ACC<br>RAM<br>RAM<br>ACC               |  |

|                          | Source (R)                     | Mask (S)                       | Destination                            |  |

| Prioritize<br>(note 1)   | RAM<br>ACC<br>D                | RAM<br>ACC<br>I<br>Ø           | RAM<br>ACC<br>Y-bus                    |  |

Note: 1. In the prioritize instructions, operand and mask must be from different sources.

| Instruction<br>Type               |                | Oper<br>Combin                        | and<br>ations       |                          |  |  |  |

|-----------------------------------|----------------|---------------------------------------|---------------------|--------------------------|--|--|--|

| Cyclic<br>Redundancy              | Data in        | Destin                                | ation               | Polynomial               |  |  |  |

| Check                             | QLINK          | RA                                    | M                   | ACC                      |  |  |  |

|                                   | Bi             | Bits Affected                         |                     |                          |  |  |  |

| Set or Reset<br>Status            | LI<br>F1<br>F1 | R, N, C<br>NK<br>ag 1<br>ag 2<br>ag 3 | <b>,</b> Z          |                          |  |  |  |

|                                   | Source         | Destination                           |                     |                          |  |  |  |

| Store<br>Status                   | Status         |                                       | RAM<br>ACC<br>Y bus |                          |  |  |  |

|                                   | Source (R)     | Source                                | (S)                 | Destination              |  |  |  |

| Load D ACC<br>Status ACC I<br>D I |                |                                       |                     | Status<br>Status and ACC |  |  |  |

| Instruction<br>Type | Operand<br>Combinations                                     |

|---------------------|-------------------------------------------------------------|

|                     | Test Condition                                              |

| Test Status         | (N#OVR)+Z N#OVR Z OVR Low C Z+C N LINK Flag 1 Flag 2 Flag 3 |

## Single Operand Instructions

Field Definitions

15 14 13 12 8

Single Operand RAM: SOR

|   | B/W | Quad | 0pcode | SRC-Dest | RAM Address |

|---|-----|------|--------|----------|-------------|

| - |     |      |        |          |             |

15 14 13 12

Single Operand Non-RAM:

|     | ,        |        |        |          |

|-----|----------|--------|--------|----------|

| B/W | Quad     | 0pcode | Source | Dest     |

|     | <u> </u> |        |        | <u> </u> |

## Opcode Specifies:

- Move

- Complement

- Increment

- Negate (i.e. two's complement)

#### Status Generated:

- Flag 3, Flag 2, Flag 1 and LINK status remain unchanged

- OVR,N,C,Z are updated

| (continned)  |

|--------------|

| Instructions |

| Operand I    |

| Single       |

| 0           | ress                  | RAM Reg 000RAM Reg 31                                                                                               | ıtion       | Y Bus<br>ACC<br>Status<br>ACC, Status                                                                       |

|-------------|-----------------------|---------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------|

|             | RAM Address           | RØØ<br>• • • R31                                                                                                    | Destination | NRY<br>NRA<br>NRS<br>NRAS                                                                                   |

| 4           |                       | 11111                                                                                                               |             | 00000<br>00001<br>00100<br>00101                                                                            |

| 2           | Dest <sup>4</sup>     | ACC<br>Y Bus<br>Status<br>RAM<br>RAM<br>RAM<br>RAM<br>RAM                                                           | R/S         | ACC<br>D<br>I<br>Ø<br>D(ØE)<br>D(SE)                                                                        |

|             | R/S <sup>4</sup>      | RAM<br>RAM<br>ACC<br>D<br>I<br>Ø<br>D(ØE)<br>D(SE)<br>RAM                                                           | R/          | AC 1                                                                                                        |

| 8           |                       | 00000 SORA<br>0010 SORY<br>0011 SORS<br>0100 SOAR<br>0110 SODR<br>0111 SOIR<br>1000 SOZR<br>1001 SOZER<br>1011 SORR |             | Ø100 SOA<br>Ø110 SOD<br>Ø111 SOI<br>1000 SOZ<br>1001 SOZE<br>1010 SOSE                                      |

| 12 9        | Opcode                | 1100 MOVE SRC> Dest 1101 COMP SRC> Dest 1110 INC SRC + 1> Dest 1111 NEG SRC + 1> Dest                               | epood0      | 1100 MOVE SRC> Dest 0<br>1101 COMP SRC> Dest 0<br>1110 INC SRC + 1> Dest 0<br>1111 NEG SRC + 1> Dest 1<br>1 |

| 15 14 13 12 | Quad3                 | 10                                                                                                                  | Quad        | 1                                                                                                           |

| 15          | B/W <sup>2</sup>      | Z B                                                                                                                 | В/м         | 9 I<br>= =<br>N                                                                                             |

|             | Instruction $^{ m 1}$ | SOR                                                                                                                 | Instruction | SONR                                                                                                        |

Notes: 1. The instruction mnemonic designates different instruction formats used in the Am29116. They are useful in assembly microcode with the System 29 AMDASM<sup>tm</sup> meta assembler.

<sup>.</sup> B = Byte Mode, W = Word Mode.

Each instruction format is divided into quadrants. These quadrants were defined mainly for convenience in classification of the instruction set and addressing modes. 3. Quad:

## Two Operand Instructions

#### Field Definitions:

$\underline{\text{Two }}\underline{\text{Operand }}\underline{\text{RAM }}\underline{1}$ (TOR1)

15 14 13 12 9 8 5 4 Ø

B/W Quad SRC-SRC Opcode RAM address

-Dest

$\underline{\text{Two }}\underline{\text{Operand }}\underline{\text{RAM }}\underline{\text{2}}$ (TOR2)

B/W Quad SRC-SRC Opcode RAM address

<u>Two Operand Non-RAM</u> (TONR)

B/W Quad SRC-SRC Opcode Dest

## Opcodes:

SUBR (S-R)

SUBRC (S-R with carry)

SUBS (R-S)

SUBSC (R-S with carry)

ADD (R+S)

ADDC (R+S with carry)

AND (R·S)

NAND  $(R \cdot S)$

EXOR (R@S)

NOR  $(\overline{R+S})$

OR (R+S)

EXNOR (ROS)

### Two Operand Instructions (continued)

### Subtraction on Am29116

Subtraction is executed by the ALU by means of an addition of the two's-complement of the subtrahend to the minuend.

That is, in general: M - S = D

minuend subtrahend difference

On the Am29116: M-S is replaced by  $M+\overline{S}+1$

The effect of this mechanism is to relate the sense of the resultant carry to the state of the borrow condition in this way:

Carry SET --> no borrow

Carry RESET --> a borrow has occurred

Similarly, a subtraction-with-carry on Am29116 is executed as an addition of the two's-complement of the subtrahend to the minuend with an adjustment based on the stored carry to properly implement a borrow:

SUBC --> M-S-borrow =  $(M+\overline{S}+1)$  if no borrow or  $(M+\overline{S}+1)-1$  if borrow

i.e. SUBC --> M-S-1+QC = M+ $\overline{S}$ +QC on Am29116

## Two Operand Instructions (continued)

#### Status Generated:

- User-definable flags remain unchanged

- LINK status remains unchanged

- For arithmetic instructions: OVR,N,C and Z status are updated

- $\bullet$  For logic instructions: N and Z status are updated. OVR and C are cleared to  $\varnothing$

|                                      | . 8         |                                        | 8                 |              | •               |          | 31        | a Territori et a <b>gila</b> n |         | -       | ***                                   | , <del>14</del> 4,,   | - ************************************ | a company company ( ) or 1 ( ) or 1 |

|--------------------------------------|-------------|----------------------------------------|-------------------|--------------|-----------------|----------|-----------|--------------------------------|---------|---------|---------------------------------------|-----------------------|----------------------------------------|-------------------------------------|

|                                      |             | SS                                     | RAM Reg 00        |              | •               |          | RAM Reg   | )                              |         |         |                                       |                       |                                        |                                     |

|                                      |             | ddre                                   | RAM               |              | •               |          | RAM       |                                |         |         |                                       |                       |                                        |                                     |

|                                      |             | RAM Address                            | RØØ               |              | •               |          | R31       |                                |         |         |                                       |                       |                                        |                                     |

|                                      |             | ~                                      | 8                 |              | •               |          |           |                                |         |         |                                       |                       |                                        |                                     |

| -                                    | 4           |                                        | ффффф             | ,            | •               |          | 11111     |                                |         |         |                                       |                       |                                        |                                     |

|                                      | 5           |                                        |                   | ج            |                 | <u>ک</u> |           | <u>ک</u>                       |         | *****   |                                       |                       |                                        | per indirection and the control     |

|                                      |             |                                        | S-R               | S-R-Cy       | R-S             | R-S-     | R+S       | R+S+                           | R.S     | R.S     | Res                                   | R+S                   | R+S                                    | Res                                 |

|                                      |             | Opcode                                 | UBR               | SUBRC        | UBS             | UBSC     | ADD       | DDC                            | N<br>S  | AND     | XOR                                   | 쏤                     | œ                                      | EXNOR                               |

|                                      |             | 8                                      | 1                 |              |                 |          |           |                                |         |         |                                       |                       |                                        |                                     |

|                                      | ω           |                                        | 000               | <b>66</b>    | 001             | ØØ1      | Ø1ØØ      | Ø1Ø                            | Ø11(    | 011     | 100                                   | 100                   | 101                                    | 101                                 |

|                                      | 6           | Dest <sup>1</sup>                      | ပ                 | ن            | ACC             | Bus      | Y Bus     | Bus                            | Σ       | Σ       | Σ                                     |                       |                                        |                                     |

|                                      |             | Be                                     | AC                | AC           | AC              | >        | >-        | >-                             | RA      | RAM     | RA                                    |                       |                                        |                                     |

|                                      |             | s <sub>1</sub>                         | )<br>)            |              | AM              | ည        |           | AM                             | ည       | н       | AM                                    |                       |                                        |                                     |

|                                      |             | R1                                     | SAM A             | <b>SAM</b>   | <u> </u>        | RAM A    | TORIY RAM | D R                            | RAM A   |         | ~                                     |                       |                                        |                                     |

|                                      |             |                                        | RAA               | RIA          | DRA             | RAY I    | RIY       | TODRY                          | TORAR F | TORIR F | TODRR [                               |                       |                                        |                                     |

| ed)                                  |             | ,                                      | Ø T0I             | Ø 10         | 1 TO            | Ø T0     | Ø T0I     | 1 TO                           | D T0    | Ø TOI   | 1 TOI                                 |                       |                                        |                                     |

| ıtinu                                | 12          |                                        | 0000              | 001          | 901             | 100      | 1010      | 101                            | 110     | 111     | 111                                   |                       |                                        |                                     |

| Two Operand Instructions (continued) | 15 14 13 12 | Quad                                   |                   |              | - <del></del>   |          | 00        |                                |         | ******  | Translation 91                        | ngama, kuranin, me ke | n cippeant in the cult                 |                                     |

| ıctio                                | 15          | B/W                                    | Marphire and when | taldam an re | , and a section | 8        | *******   | 3                              | ~~~~~   |         |                                       |                       | -enomic                                | Lengthy, and X1                     |

| nstri                                |             | В,                                     |                   |              |                 | <br> 0   |           | "<br>H                         |         |         | · · · · · · · · · · · · · · · · · · · |                       |                                        |                                     |

| I put                                |             | ion                                    |                   |              |                 |          |           |                                |         |         |                                       |                       |                                        |                                     |

| Opera                                |             | Instruction                            |                   |              |                 |          | T0R1      |                                |         |         |                                       |                       |                                        |                                     |

| ) OM                                 |             | Inst                                   |                   |              |                 |          |           |                                |         |         |                                       |                       |                                        |                                     |

| - 1                                  | ,           | ــــــــــــــــــــــــــــــــــــــ |                   |              |                 |          |           |                                |         | ,       |                                       |                       |                                        | ·                                   |

Dest = Destination S = Source,

Two Operand Instructions (continued)

| Instruction              | B/W                  | Quad         |      |           | ~   | S       | R S Dest              | 0pcode |                     | RAM A | RAM Address |

|--------------------------|----------------------|--------------|------|-----------|-----|---------|-----------------------|--------|---------------------|-------|-------------|

|                          | 6                    |              | 9001 | TODAR     | 0   | ACC RAM | RAM                   |        | <i>ወወወወወ</i> RØØ    | RØØ   | RAM Reg ØØ  |

| TOR2                     |                      | 10           | 0010 | TOAIR ACC | ACC | ш       | RAM                   | Note 1 | •                   | •     | •           |

|                          | <b>3</b><br>∥<br>⊢   |              | Ø1Ø1 | TODIR D   | ۵   | Н       | RAM                   |        | 11111               | R31   | RAM Reg 31  |

|                          |                      |              |      |           | ~   | S       |                       |        |                     | Desti | Destination |

| , 1                      |                      |              | 0001 | TODA      | 0   | ACC     |                       |        | <i><b>ФФФФФ</b></i> | NRY   | Y Bus       |

| TONR                     | 3 -<br>11            | H            | ØØ1Ø | TOAI      | ACC | H       | anaine an Airin Marin | Note 1 | 99991               | NRA   | ACC         |

| nd Agrand a Market and a | <b>≼</b><br>  <br> - | and a second | 0101 | TODI      | 0   | ы       |                       |        | 90100               | NRS   | Status      |

|                          |                      |              |      |           |     |         |                       |        | 00101               | NRAS  | ACC, Status |

Note 1: Opcodes are the same as for TOR1 (see previous page).

## Single Bit Shift Instructions

- Operate in Byte or Word Mode.

- You can specify direction and shift linkage.

Field Definitions:

15 14 13 12 9 8 5 4 Ø

<u>Shift RAM: SHFTR</u> B/W Quad SRC-Dest Opcode RAM address

Shift Non-RAM: SHFTNR B/W Quad SRC Opcode Destination

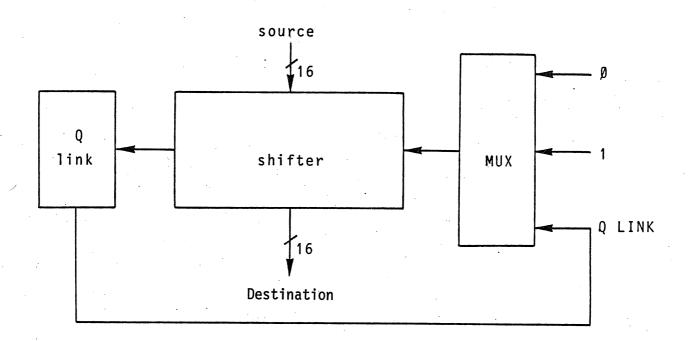

Shift Up Function

In Word Mode:

$\mathrm{Dest}_i$  <--  $\mathrm{SRC}_{i-1}$  for i=1 to 15  $\mathrm{Dest}_\emptyset$  <-- Shift Input

In Byte Mode:

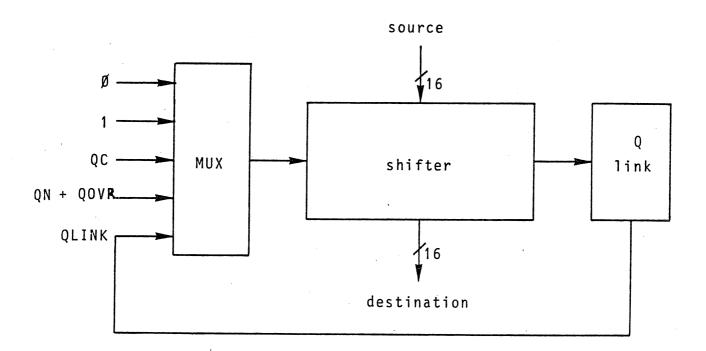

#### Shift Down Function

In Word Mode:

$\mathsf{Dest}_i$  <--  $\mathsf{SRC}_{i+1}$  for  $i=\emptyset$  to 14  $\mathsf{Dest}_{15}$  <--  $\mathsf{Shift}$  Input

In Byte Mode:

### Opcode specifies:

- Shift direction

- up (multiply by 2)

- down (divide by 2)

- Shift linkage

- $\emptyset$ ,1,QLINK are selectable in both directions

- QC,QN@QOVR are selectable in down shifts only

#### Status generated:

- User-definable flags remain unchanged

- Z is updated

- OVR and C are forced to zero

- LINK and N depend on direction and Byte/Word mode (shifted output is always loaded into the QLINK):

| Direction | Byte/Word | LINK              | N                 |

|-----------|-----------|-------------------|-------------------|

| Up        | W         | SCR <sub>15</sub> | SRC <sub>14</sub> |

| OP .      | В         | SRC <sub>7</sub>  | SRC <sub>6</sub>  |

| Down      | W         | SRC <sub>Ø</sub>  | Shift Input       |

| Domi      | В         | SRC <sub>Ø</sub>  | Shift Input       |

Appropriate Usage of the Shift Input:

- QLINK for multiple-word shifts.

- QN@QOVR for two's-complement multiplication.

That is, in the accumulation of each stage of the partial product an overflow may occur. In the case of an overflow the sign bit is incorrect. Hence, as the next down shift is executed, the sign extension is to be taken as the complement of the incorrect sign bit.

In the case in which overflow does not occur, the sign bit is correct as it stands. Hence, as the next down shift is executed, the sign bit is extended directly.

The Exclusive OR of the N bit with the OVR bit produces the correct sign extension in all cases.

Single Bit Shift Instructions (continued)

|             | <del>,</del>   |             |                |          |             |       |       | *************************************** | ·           | <del></del>           | ****                |

|-------------|----------------|-------------|----------------|----------|-------------|-------|-------|-----------------------------------------|-------------|-----------------------|---------------------|

| RAM Address | RØØ RAM Reg ØØ |             | R31 RAM Reg 31 |          |             |       |       |                                         | Destination | Ø NRY Y Bus           | 1 NRA ACC           |

|             | 00000          | •           | 11111          |          |             |       |       |                                         | Ō           | ø<br>Ø<br>Ø<br>Ø<br>Ø | 99991               |

|             | 0              | <del></del> | QLINK          | 8        | н           | QLINK | ၁၀    | QN@QOVR                                 |             |                       | ¥                   |

|             | dn             | dn          | dn             | Down     | Down        | Down  | Down  | Down                                    |             | , F                   | 1 JHC 1             |

| 0pcode      | SHUPZ          | SHUP1       | SHUPL          | SHDNZ    | SHDN1       | SHDNL | SHDNC | SHDNOV                                  | 0pcode      |                       | Jaille as IUF JUFIK |

|             | ወወወወ           | 0001        | ØØ1Ø           | Ø1ØØ     | Ø1Ø1        | Ø11Ø  | 0111  | 1000                                    |             | ,                     | ਰ<br>ਨ              |

| Dest        | RAM RAM        | RAM         |                |          |             |       |       |                                         |             |                       |                     |

| LJ          | l              |             |                |          |             |       | _     |                                         | CJ.         | ACC                   | ۵                   |

|             | Ø11Ø SHRR      | SHDR        |                |          | •           |       |       |                                         |             | SHA                   | SHD                 |

|             | Ø11Ø           | Ø111        |                |          |             |       |       |                                         |             | Ø11Ø SHA              | Ø111                |

| Quad        |                |             |                | 6        | <b>⊋</b>    |       |       |                                         | Quad        | 11                    | -1<br>-1            |

| B/W         |                |             |                | 8<br>= 0 | T =         |       |       |                                         | B/W         | Ø = B                 | 1 = W               |

| Instruction |                |             |                | CUETD    | 7<br>7<br>7 |       |       |                                         | Instruction | CUETND                |                     |

Note: 1. U = Source

### Bit Oriented Instructions

Field Definitions

15 14 13 12 9 8

5 4

Bit Oriented RAM 1: BOR1 Bit Oriented RAM 2: BOR2 B/W Quad RAM address n Opcode

15 14 13 12 9 8

5 4

Bit Oriented Non-RAM: BONR

| B/W      | Quad | n | 0pcode | RAM address |

|----------|------|---|--------|-------------|

| <u> </u> |      |   |        |             |

• "n" is the address of bit position within word:

15 14 13 12 11 1Ø 9 8 7 6 5 3 2 1 Ø

• Opcodes:

Set Bit n

1 --> n<sup>th</sup> bit

Reset Bit n

Ø --> n<sup>th</sup> bit

Test Bit n

set Z status from bit n

Load 2<sup>n</sup> Load 2<sup>n</sup>

$1 \longrightarrow bit n$ ,  $\emptyset \longrightarrow all other bits$  $\emptyset$  --> bit n, 1 --> all other bits

Incr by 2<sup>n</sup>

$SRC + 2^n \longrightarrow SRC$

Decr by 2<sup>n</sup>

$SRC - 2^n \longrightarrow SRC$

## Bit Oriented Instructions (continued)

#### Status generated:

- User-definable flags remain unchanged

- N: is always updated

- Z: is updated after RESET, TEST, INCREMENT, DECREMENT

- is cleared after SET or LOAD

- OVR and C: are updated after INCREMENT or DECREMENT

- are forced to zero after SET, RESET, TEST, LOAD

Bit Oriented Instrucțions (continued)

| Quad    | E      |           | Opcode     |                          |       | RAM | RAM Address    |

|---------|--------|-----------|------------|--------------------------|-------|-----|----------------|

|         |        | 1101      | SETNR      | Set RAM, bit n           | 00000 | RØØ | RØØ RAM Reg ØØ |

| Ø to 15 | ى<br>ك | 1110      | 1110 RSTNR | Reset RAM, bit n         | •     | •   | •              |

|         |        | 1111      | TSTNR      | Test RAM, bit n          | 11111 | R31 | RAM Reg 31     |

| ב       |        |           | 0pcode     |                          |       | RAM | RAM Address    |

|         | 1      | 1100      | 1100 LD2NR | 2 <sup>n</sup> > RAM     | 00000 | RØØ | RØØ RAM Reg ØØ |

| ÷       | L      | 1101      | L DC2NR    | 27> RAM                  | •     | •   | •              |

| 3       | U.     | 1110      | A2NR       | RAM+2 <sup>n</sup> > RAM | 11111 | R31 | RAM Reg 31     |

|         | -      | 1111 S2NR | SZNR       | RAM-2 <sup>n</sup> > RAM |       |     |                |

source register = destination register Normally: Note:

With additional external MUX you can specify another destination register

## Bit Oriented Instructions (continued)

| Instruction | B/W            | Quad | n       | Opcode <sup>1</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|----------------|------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BONR        | Ø = B<br>1 = W | 11   | Ø to 15 | ΦΦΦΦΦ         TSTNA         Test ACC, bit n           ΦΦΦΦ1         RSTNA         Reset ACC, bit n           ΦΦΦ1Φ         SETNA         Set ACC, bit n           ΦΦ1ΦΦ         A2NA         ACC+2 <sup>n</sup> > ACC           ΦΦ11Φ         LD2NA         2 <sup>n</sup> > ACC           ΦΦ111         LDC2NA         2 <sup>n</sup> > ACC           ΦΦ111         LDC2NA         2 <sup>n</sup> > ACC           1ΦΦΦ         TSTND         Test D, bit n           1ΦΦΦ         TSTND         Reset D, bit n           1ΦΦΦ         SETND         Set D, bit n           1Φ1Φ         A2NDY         D+2 <sup>n</sup> > Y Bus           1Φ1Φ         LS2NY         2 <sup>n</sup> > Y Bus           1Φ110         LS2NY         2 <sup>n</sup> > Y Bus           1Φ111         LDC2NY         2 <sup>n</sup> > Y Bus |

Note 1: In this format the opcode field contains both source and destination.

#### Rotate By n Bits Instructions

#### Field Definitions:

15 14 13 12 9 8 5 4 Rotate RAM 1: ROTR1 B/W Quad SRC-Dest RAM address Rotate RAM 2: ROTR2 15 14 13 12 9 8 5 4 Rotate Non-RAM: ROTNR B/W Quad 11ØØ SRC-Dest

- $\bullet$  "n" is the number of positions to shift:

- n is in the range  $\emptyset$  to 15 in word mode

- n is in the range  $\emptyset$  to 7 in byte mode

- There is no explicit opcode for n-bit rotates.

- These instructions rotate <u>up</u>.

To rotate down by "i" bits: n=16-i or 8-i

- Source is always presented to the U-MUX of the ALU

## Rotate by n Bits Instructions (continued)

Example: n = 3 ... rotate <u>up</u> by 3 bit positions

#### • Word Mode:

Destination 1  $\emptyset$   $\emptyset$  1 1  $\emptyset$  1 1 1 1 1 1 1  $\emptyset$   $\emptyset$   $\emptyset$

### • Byte Mode:

Destination  $\emptyset$   $\emptyset$   $\emptyset$  1  $\emptyset$   $\emptyset$  1 1 1 1 1 1 1  $\emptyset$  1 1

## Rotate by n Bits Instructions (continued)

Status generated:

- User-definable flags remain unchanged.

- OVR and C are forced to zero.

- N and Z are updated to correspond to resulting byte or word.

That is, the N bit of the status byte becomes:

$SRC_{15-n}$  in Word Mode

${\tt SRC_{8-n}}$  in Byte Mode

Rotate By n Bits Instructions (continued)

|                   | T           |                   |                |                                   | Γ                 |              |                  |                   | <del>                                     </del> |              |

|-------------------|-------------|-------------------|----------------|-----------------------------------|-------------------|--------------|------------------|-------------------|--------------------------------------------------|--------------|

| S                 | Reg ØØ      | :                 | Reg 31         |                                   | v                 | Reg ØØ       | Reg 31           | Dest <sup>1</sup> | Y Bus<br>ACC                                     | Y Bus<br>ACC |

| RAM Address       | RAM         | •                 | RAM            |                                   | RAM Address       | RAM          | RAM              | LJ                | م م                                              | ACC<br>ACC   |

| RAM A             | RØØ         | •                 | R31            |                                   | RAM A             | RØØ          | R31              |                   | RTDY<br>RTDA                                     | RTAY<br>RTAA |

|                   | <i>фффф</i> | •                 | 11111          |                                   |                   | <b>ØØØØØ</b> | 11111            |                   | 11000                                            | 11100        |

| $\mathtt{Dest}^1$ | ACC         | Y Bus             | RAM            | <del>10000.</del> 20 <u>3</u> 01. | $\mathtt{Dest}^1$ | RAM          | RAM              |                   |                                                  |              |

| u1                | RAM         | RAM               | RAM            |                                   | LJ                | ACC          |                  |                   |                                                  |              |

|                   | RTRA        | RTRY              | RTRR           |                                   |                   | RTAR         | RTDR             |                   |                                                  | ·            |

|                   | 1100        | 1110              | 1111           |                                   |                   | 0000         | 0001             |                   |                                                  | 1100         |

| u                 |             | Ø to 15           |                |                                   | u                 | 15 4 6       | CT 01            | u                 |                                                  | 0 to 15      |

| Quad              |             | Ø                 |                |                                   | Quad              | 10           | -i<br>->         | Quad              |                                                  | Ħ            |

| B/W               | ۵<br>ا<br>و | 0 =<br>1  <br>3 - | <b>≼</b><br>II |                                   | B/W               | Ø = B        | ]<br> <br>       | B/W               | Ø = B                                            | 1 = M        |

| Instruction       | -           | ROTR1             |                |                                   | Instruction       | Catoa        | N<br>N<br>N<br>N | Instruction       |                                                  | ROTNR        |

Note 1: U = Rotated Source Dest = Destination

## Rotate and Merge Instructions

Field Definition:

- n is the number of positions to upshift operand U

- Operand R remains unrotated

- Use mask M to select bits:

Destination<sub>i</sub> =

$$U_i$$

if  $M_i$  = 1

Destination<sub>i</sub> =  $R_i$  if  $M_i$  =  $\emptyset$

- $\bullet$  There is no explicit opcode for ROTM

- Choose one of six possible triplets for the two operands and the mask

# ROTATE AND MERGE INSTRUCTIONS (continued)

### Rotate and Merge Instructions (continued)

#### Examples:

n = 4 Word Mode

U:  $\emptyset \emptyset 11 \emptyset \emptyset \emptyset 1 \emptyset 1 \emptyset 1 \emptyset 1 1 \emptyset$

Rotated U:  $\emptyset \emptyset \emptyset 1 \emptyset 1 \emptyset 1 \emptyset 1 1 \emptyset \emptyset \emptyset 1 1$

R: 1 Ø 1 Ø 1 Ø 1 Ø 1 Ø 1 Ø 1 Ø

Mask S:  $\emptyset \emptyset \emptyset \emptyset 11111 \emptyset \emptyset \emptyset \emptyset 11111$

(= R R R R U U U U R R R R U U U U)

Dest (R): 1 Ø 1 Ø Ø 1 Ø 1 1 Ø 1 Ø Ø Ø 1 1

n = 4 Byte Mode

U:  $\emptyset \emptyset \emptyset 1 \emptyset \emptyset 1 \emptyset 1 1 1 1 1 1 1 1 \emptyset$

Rotated U:  $\emptyset \emptyset \emptyset 1 \emptyset \emptyset 1 \emptyset 1 1 1 1 \emptyset 1 1 1 1 1$

R: 1111 1110 0001 0000

(= RURU RURU RURU RURU)

Y-bus: x x x x x x x x x x 0 1 0 0 0 1 0 1

Dest (R): 1 1 1 1 1 1 1 0 0 1 0 0 0 1 0 1

Rotate and Merge Instructions (continued)

| Instruction | B/W           | Quad | u       |      | ,    | $0^{1}$ | $	t R/	ext{Dest}^1$ | $S^1$ |                     | RAM A    | Address   | l  |

|-------------|---------------|------|---------|------|------|---------|---------------------|-------|---------------------|----------|-----------|----|

|             |               |      |         | Ø111 | MDAI | ٥       | ACC                 | П     |                     |          |           | 1  |

|             |               |      |         | 1000 | MDAR | _       | ACC                 | RAM   | <i><b>ФФФФФ</b></i> | 89<br>89 | RAM Reg ( | 8  |

|             | 0<br>= B      |      |         | 1001 | MDRI | ۵       | RAM                 | Н     | •                   | •        | •         | •  |

| ROTM        |               | 01   | Ø to 15 | 1010 | MDRA | ۵       |                     | ACC   | 11111               | R31      | RAM Reg 3 | 31 |

|             | 3<br>  <br> - |      |         | 1100 | MARI | ACC     |                     | Н     |                     |          | •         |    |

|             |               |      |         | 1110 | MRAI | RAM     | _                   | Н     |                     |          |           |    |

Note 1: U = Rotated Source R/Dest = Non-Rotated Source and Destination S = Mask

## Rotate and Merge Instructions (continued)

## Status generated:

- User-definable flags remain unchanged

- LINK status remains unchanged

- OVR and C are forced to zero

- Z and N are updated to reflect the resulting word or byte

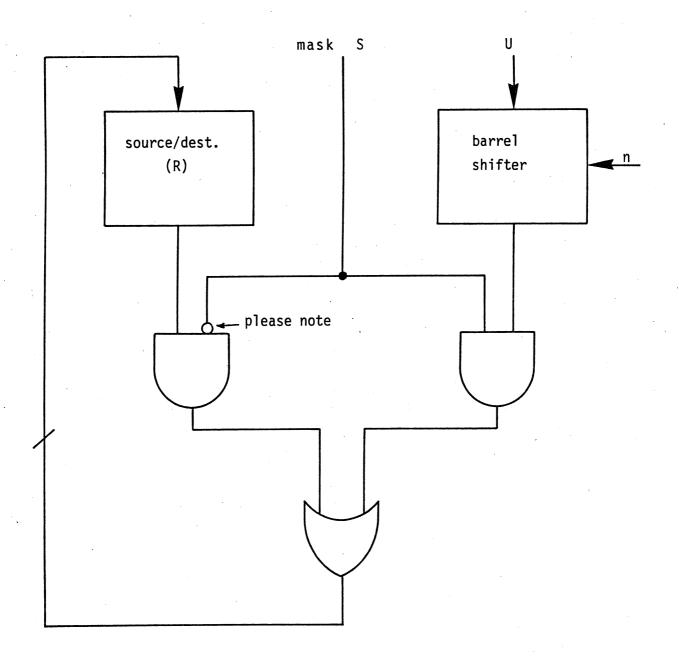

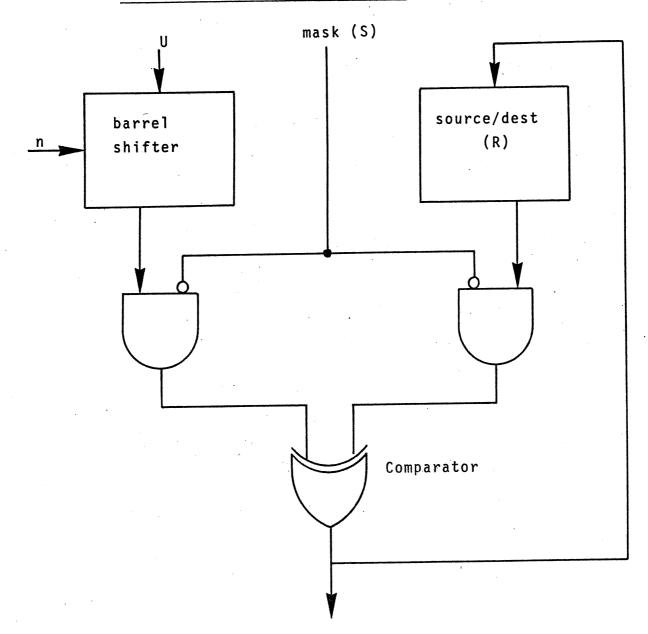

#### Rotate and Compare Instructions

Field Definitions

iela bei illicions

15 14 13 12 9 8

4

Ø

Rotate and Compare: ROTC

| B/W | Quad | n | Rot SRC-<br>Non Rot SRC-<br>Mask | RAM address |

|-----|------|---|----------------------------------|-------------|

|-----|------|---|----------------------------------|-------------|

- ullet n is the number of positions to upshift operand U

- Operand R is unrotated

- (Rotated U AND Mask) EXOR (R AND Mask)

- There is no explicit opcode for ROTC

- Choose one of four possible triplets for the two operands and the mask

# ROTATE AND COMPARE INSTRUCTION (continued)

Destination & Zero-Detect Logic

## Rotate and Compare Instructions (continued)

#### Examples:

n = 4 Word Mode

U: Ø Ø 1 1 Ø Ø Ø 1 Ø 1 Ø 1 Ø 0 1 Ø

Rotated U:  $\emptyset \emptyset \emptyset 1$   $\emptyset 1 \emptyset 1$   $\emptyset 1 1 \emptyset$   $\emptyset \emptyset 1 1$

R: Ø Ø Ø 1 Ø 1 Ø 1 1 1 1 1 Ø Ø Ø Ø

Mask S:  $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$  1 1 1 1 1 1 1 1 1 1 1 ...select HI byte

Dest:  $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$  1  $\emptyset$  0 1  $\emptyset$  0 1 1 & Z status= $\emptyset$  ...i.e. does not match

Mask S: 1 1 1 1 1 1 1 1 1 0  $\emptyset$  1  $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$  ...select various bits

Dest:  $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$   $\emptyset$  1  $\emptyset$   $\emptyset$  1  $\emptyset$   $\emptyset$  1 & Z Status= $\emptyset$  ...i.e. does not match

Rotate and Compare Instructions (continued)

| nstruction | B/W   | Quad | <b>c</b> |              |      | <sup>1</sup> | R/Dest <sup>1</sup> | 1 S1     |                     | RAM A | Address    |

|------------|-------|------|----------|--------------|------|--------------|---------------------|----------|---------------------|-------|------------|

|            | Ø = B |      |          | 0010<br>0011 | CDAI | 00           | ACC                 | Н        | <i><b>ФФФФФ</b></i> | RØØ . | RAM Reg ØØ |

| ROTC       | 11    | Ø1   | Ø to 15  | Ø1ØØ<br>Ø1Ø1 | CDRA | RAM          | RAM                 | ACC<br>I | 11111               | R31   |            |

S = Mask R/Dest = Non-Rotated Source and Destination

U = Rotated Source

Note 1:

Status generated:

User definable flags remain unchanged Link status remains unchanged OVR and C are forced to zero N and Z are updated

## Prioritize Instructions

#### Field Definitions:

|                                                             | 15  | 14 13 | 12 9        | 8 5         | 4 Ø                         |

|-------------------------------------------------------------|-----|-------|-------------|-------------|-----------------------------|

| <u>Pr</u> iori <u>t</u> ize RAM <u>1</u> : PRT1             | B/W | Quad  | Destination | Source (R)  | RAM Address/<br>Mask (S)    |

|                                                             |     |       |             |             |                             |

| <u>Pr</u> iori <u>t</u> ize RAM <u>2</u> : PRT2             | B/W | Quad  | Mask (S)    | Destination | RAM Address/<br>Source (R)  |

|                                                             |     | -     |             |             |                             |

| <u>Pr</u> iori <u>t</u> ize RAM <u>3</u> : PRT3             | B/W | Quad  | Mask (S)    | Source (R)  | RAM Address/<br>Destination |

|                                                             |     |       | ,           |             |                             |

| <u>Pr</u> iori <u>t</u> ize <u>N</u> on- <u>R</u> AM: PRTNR | B/W | Quad  | Mask (S)    | Source (R)  | Destination                 |

Note: there is no explicit opcode for prioritize instructions.

Remember the logic diagram of the AM 29116:

- The input to the priority encoder comes from the output of the ALU.

- ALU operation:

- . the operand is applied to the R-port

- . the mask is applied to the S-port

- . the ALU calculates: Operand AND  $\overline{\text{Mask}}$

- mask bit =  $\emptyset$  Passes the operand bit

- The output of the priority encoder is a 5-bit binary code indicating the bit position of the highest priority active bit. That is, the output designates the most significant unmasked bit.

## Word Mode

| Highest Priority<br>Active Bit | Encoder<br>Output |                                |

|--------------------------------|-------------------|--------------------------------|

| NONE                           | Ø                 |                                |

| 15                             | 1                 |                                |

| 14                             | 2                 |                                |

| •                              | •                 | .i.e. output is 16-n           |

| •                              | •                 | where n is the position of the |

| •                              | •                 | highest priority active bit    |

| 1                              | 15                |                                |

| Ø                              | 16                |                                |

# Byte Mode

| Highest Priority<br>Active Bit | Encoder<br>Output |                                      |

|--------------------------------|-------------------|--------------------------------------|

| NONE                           | Ø                 |                                      |

| 7                              | 1                 |                                      |

| 6                              | 2                 |                                      |

| •                              | •                 | .i.e. output is 8-n                  |

| •                              |                   | where n is the position of the       |

| •                              | •                 | highest priority active bit          |

| 1                              | 7                 |                                      |

| Ø                              | 8                 | Note that the upper byte is ignored. |

Examples:

#### Word Mode

| Operand:    | 15 12<br>Ø Ø Ø 1 | 11 8<br>Ø Ø 1 Ø | 7 4<br>Ø Ø 1 Ø | •     | Ø |

|-------------|------------------|-----------------|----------------|-------|---|

| Mask:       | 1 1 1 1          | Ø Ø Ø Ø         | 1 1 1 1        | ØØØ   | ø |

| ALU result: | Ø Ø Ø Ø          | Ø Ø 1 Ø         | Ø Ø Ø Ø        | 1 Ø 1 |   |

Highest priority active bit is in position 9.

Priority result = 16 - 9 = 7

#### Byte Mode

| Operand:    | 15 12<br>Ø Ø Ø 1 |         | 7 4<br>Ø Ø 1 Ø | 3<br>1 Ø | Ø<br>1 Ø |

|-------------|------------------|---------|----------------|----------|----------|

| Mask:       | 1 1 1 1          | Ø Ø Ø Ø | 1 1 1 1        | ØØ       | ØØ       |

| ALU result: | Not in           | olved/  | ØØØØ           | 1 Ø      | 1 Ø      |

Highest priority active bit is in position 3.

Priority result = 8 - 3 = 5

Prioritize Instructions (continued)

| RAM Address/Mask(S) | 00000 R00 RAM Reg 00                                   | RAM Address/Source(R) | 00000 R00 RAM Reg 00<br>11111 R31 RAM Reg 31 |

|---------------------|--------------------------------------------------------|-----------------------|----------------------------------------------|

| (                   | ACC<br>D                                               | on                    | ACC<br>Y Bus                                 |

| Source (R)          | PRT1A<br>PR1D                                          | Destination           | PR2A<br>PR2Y                                 |

| Sou                 | Ø111<br>1ØØ1                                           | Des                   | 9999<br>9919                                 |

| on                  | ACC<br>Y Bus<br>RAM                                    |                       | ACC<br>Ø<br>I                                |

| Destination         | PR1A<br>PR1Y<br>PR1R                                   | Mask (S)              | PRA<br>PRZ<br>PRI                            |

| Des                 | 1 <i>000</i><br>1 <i>0</i> 1 <i>0</i><br>1 <i>0</i> 11 | Ma                    | 1000<br>1010<br>1011                         |

| Quad                | 10                                                     | Quad                  | 10                                           |

| B/W                 | Ø = B<br>1 = W                                         | В/м                   | 1.0<br>1.0<br>1.0                            |

| Instruction B/W     | PRT1                                                   | Instruction           | PRT2                                         |

Prioritize Instructions (continued)

| SE                                   |

|--------------------------------------|

| 100 PRA<br>10 1010 PRZ<br>1011 PRI   |

| Quad Mask (S)                        |

| 10000 PRA<br>11 1010 PRZ<br>1011 PRI |

#### Status generated:

- User-definable flags remain unchanged

- Link status remains unchanged

- OVR and C are forced to zero

- N and Z are updated to reflect the result

#### Use this instruction in:

- Selecting the next request to be serviced out of several active requests for service.

- Arithmetic operations (multiplication, normalization) to shorten the number of microcycles. (not available on Am2901/2903/29203's!)

- N-way branching

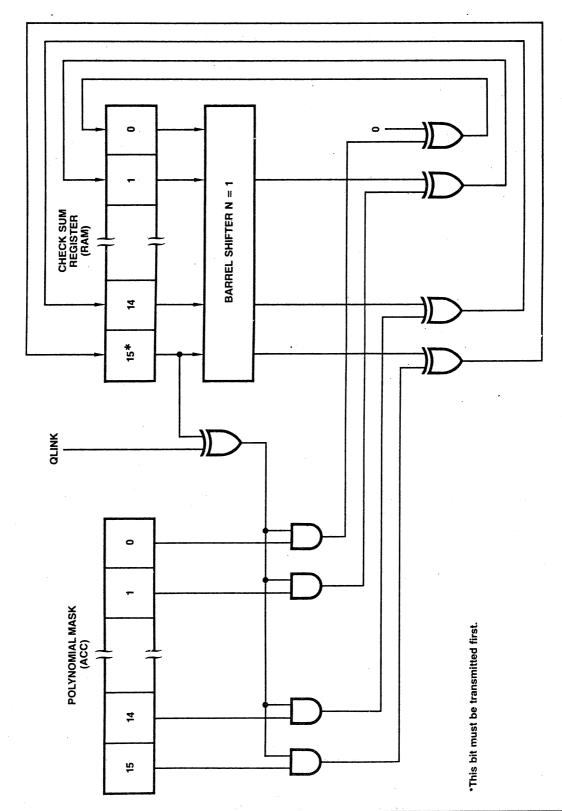

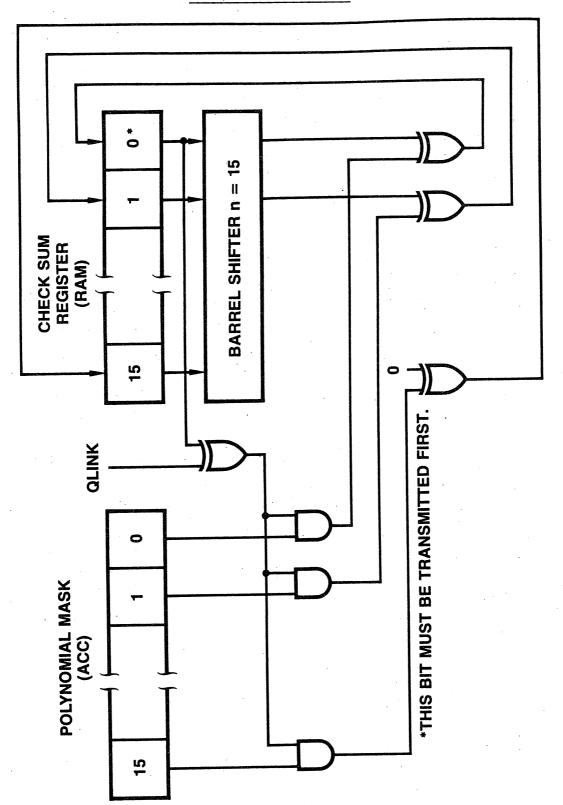

#### **CRC** Instructions

• Am29116 generates CRC check bits for any polynomial with a remainder of 16 bits or less

(80 to 95% of CRC calculations use 16-bit remainders)

- Two CRC calculations are available:

- · CRC forward checksum bit 15 is to be transmitted first

- ullet CRC reverse checksum bit  $oldsymbol{arphi}$  is to be transmitted first

- CRC calculations are done in word mode.

However, the active number of bits in the remainder may be less than 16.

## CRC Forward Function

CRC Reverse Function

Using the CRC instructions to calculate the CRC remainder for a message:

- Place the polynomial mask in the ACC.

- Initialize check sum register in RAM to zero (in most cases).

- Generating a CRC remainder for a k-bit message takes >2k cycles.

For each bit of the message, m<sub>j</sub> you execute 2 instructions:

- Shift the bit into the LINK status bit by means of a single-bit shift instruction.

- Execute a CRCF or CRCR instruction. This will update the remainder in RAM in accordance with the current bit.

Mathematically, for the  $i^{th}$  message bit  $m_i$ , the 'j' CRC remainder bits  $C_{i,j}$  are generated as follows:

$$(\mathsf{m_i} \oplus (\mathsf{C_{i-1,15}} \cdot \mathsf{Mask_j})) \oplus \mathsf{C_{i-1,j-1}} \xrightarrow{-->} \mathsf{C_{i,j}} \qquad \dots \text{ for } \mathsf{j=1} \text{ thru } \mathsf{15}$$

$$\mathsf{m_i} \oplus (\mathsf{C_{i-1,15}} \cdot \mathsf{Mask_\emptyset}) \xrightarrow{-->} \mathsf{C_{i,\emptyset}} \qquad \dots \text{ for } \mathsf{bit} \ \emptyset$$

- Of course, further instructions will have to be used, generally every 8 or 16 bits, to fetch another byte or word of the message from a source outside the Am29116.

- With the microcycle of 100 ns the Am29116 is able to generate CRC bits at a rate of 5 MHz.

Deriving the CRC Mask from the Polynomial: CRC Forward Instruction

|                                                                  | 1        |      |         |    |    | Ma | ısk    | Bit    | Po      | sit      | ion    |        |         |          |   |   |   |               |

|------------------------------------------------------------------|----------|------|---------|----|----|----|--------|--------|---------|----------|--------|--------|---------|----------|---|---|---|---------------|

|                                                                  |          | 15   | 14      | 13 | 12 | 11 |        | 9      | 8       | 7        | 6      | 5      | 4       | 3        | 2 | 1 | Ø |               |

|                                                                  |          |      |         |    |    | L  | Coe    | ffi    | cie     | nts      |        |        |         | L        |   |   |   | 29116         |

| Polynomial                                                       | 16       | 15   | 14      | 13 | 12 | 11 | 1ø     | 9      | 8       | 7        | 6      | 5      | 4       | 3        | 2 | 1 | Ø | Mask<br>(hex) |

| CRC-16<br>x16+x15+x2+1                                           | 1        | 1    | Ø       | Ø  | Ø  | Ø. | Ø      | Ø      | Ø       | Ø        | Ø      | Ø      | Ø       | Ø        | 1 | Ø | 1 | 8ØØ5          |

| CRC-16 Reverse<br>x <sup>16</sup> +x <sup>14</sup> +x+1          | 1        | Ø    | 1       | Ø  | Ø  | Ø  | Ø      | Ø      | Ø       | Ø        | Ø      | Ø      | Ø       | Ø        | Ø | 1 | 1 | 4ØØ3          |

| CRC-CCITT<br>x <sup>16</sup> +x <sup>12</sup> +x <sup>5</sup> +1 | 1        | Ø    | Ø       | Ø  | 1  | Ø  | Ø      | Ø      | Ø       | Ø        | Ø      | 1      | Ø       | ø        | Ø | Ø | 1 | 1ø21          |

| CRC-CCITT Reverse                                                | 1        | Ø    | Ø       | Ø  | Ø  | 1  | Ø      | Ø      | Ø       | Ø        | Ø      | Ø      | 1       | Ø        | Ø | Ø | 1 | Ø811          |

| CRC-12<br>x12+x11+x3+x2+x+1                                      | (12<br>1 | 11 1 | 1Ø<br>Ø |    |    |    | 6<br>Ø | 5<br>Ø | 4<br>Ø  | 3        | 2<br>1 | 1<br>1 | Ø)<br>1 | *<br>  Ø | Ø | Ø | Ø | 8ØFØ          |

| LRC-8<br>x <sup>8</sup> +1                                       | (8<br>1  |      |         |    |    | 1  | 2<br>Ø | 1<br>Ø | Ø)<br>1 | *<br>  Ø | Ø      | Ø      | Ø       | Ø        | Ø | Ø | Ø | Ø1ØØ          |

\* Note: The coefficients for the short polynomials, CRC-12 and LRC-8, are left-justified.

Deriving the CRC Mask from the Polynomial: CRC Reverse Instruction

| •                                                                               |    |    |    |    |         | Ма | sk     | Bit | Ро      | sit    | ior    | 1      |          |        |         |        |             |               |

|---------------------------------------------------------------------------------|----|----|----|----|---------|----|--------|-----|---------|--------|--------|--------|----------|--------|---------|--------|-------------|---------------|

|                                                                                 | 15 | 14 | 13 | 12 | 11      | 1Ø | 9      | 8   | 7       | 6      | 5      | 4      | 3        | 2      | 1       | Ø      |             |               |

|                                                                                 |    |    |    |    |         |    | Coe    | ffi | cie     | nts    |        |        |          |        |         |        |             | 29116<br>Mask |

| Polynomial                                                                      | Ø  | 1  | 2  | 3  | 4       | 5  | 6      | 7   | 8       | 9      | 1ø     | 11     | 12       | 13     | 14      | 15     | 16          | (hex)         |

| $_{x}^{CRC-16}$                                                                 | 1  | Ø  | 1  | Ø  | Ø       | Ø  | Ø      | Ø   | Ø       | Ø      | Ø      | Ø      | Ø        | Ø      | Ø       | 1      | 1           | AØØ1          |

| CRC-16 Reverse<br>x <sup>16</sup> +x <sup>14</sup> +x+1                         | 1  | 1  | Ø  | Ø  | Ø       | Ø  | Ø      | Ø   | Ø       | Ø      | Ø      | Ø      | Ø        | Ø      | 1       | Ø      | 1           | CØØ2          |

| CRC-CCITT<br>x16 <sub>+x</sub> 12 <sub>+x</sub> 5 <sub>+1</sub>                 | 1  | Ø  | Ø  | Ø  | Ø       | 1  | Ø      | Ø   | Ø       | Ø      | Ø      | Ø      | 1        | Ø      | Ø       | Ø      | 1           | 84Ø8          |